Titled “Precise and low-power closed-loop neuromodulation through algorithm-integrated circuit co-design”, this contribution has been published in the Frontiers in Neuroscience. In this paper, we undertake an algorithm-integrated circuit co-design approach for close-loop control with dedicated integrated circuits to address the issues related to false alarm rates and power consumption.

Congratulations to our Research Associate Professor Jie Yang and to this paper’s co-authors for this excellent achievement.

Reference:

YANG J., ZHAO S., WANG J., LIN S., HOU Q., SAWAN M., "Precise and Low-power Closed-Loop Neuromodulation through Algorithm-Integrated Circuit Co-Design”, Frontiers in Neuroscience Journal, Vol. 18, 2024

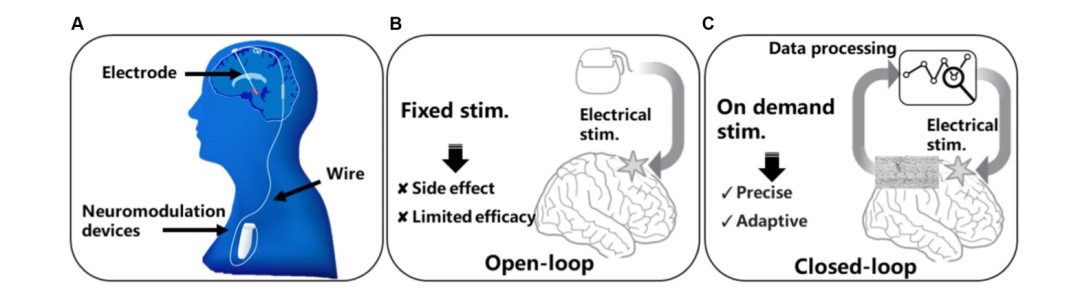

Figure 1. Neuromodulation modalities: (A) conventional DBS device, (B) open-loop neuromodulation, (C) closed-loop neuromodulation.

Figure 2.Test system and chip photograph, (A) test system with GUI, FPGA platform and PCB board, (B) microphotograph of the proposed chip.

Abstract:

Implantable neuromodulation devices have significantly advanced treatments for neurological disorders such as Parkinson’s disease, epilepsy, and depression. Traditional open-loop devices like deep brain stimulation (DBS) and spinal cord stimulators (SCS) often lead to overstimulation and lack adaptive precision, raising safety and side-effect concerns. Next-generation closed-loop systems offer real-time monitoring and on-device diagnostics for responsive stimulation, presenting a significant advancement for treating a range of brain diseases. However, the high false alarm rates of current closed-loop technologies limit their efficacy and increase energy consumption due to unnecessary stimulations. In this study, we introduce an artificial intelligence-integrated circuit co-design that targets these issues and using an online demonstration system for closed-loop seizure prediction to showcase its effectiveness. Firstly, two neural network models are obtained with neural-network search and quantization strategies. A binary neural network is optimized for minimal computation with high sensitivity and a convolutional neural network with a false alarm rate as low as 0.1/h for false alarm rejection. Then, a dedicated low-power processor is fabricated in 55 nm technology to implement the two models. With reconfigurable design and event-driven processing feature the resulting application-specific integrated circuit (ASIC) occupies only 5mm2 silicon area and the average power consumption is 142 μW. The proposed solution achieves a significant reduction in both false alarm rates and power consumption when benchmarked against state-of-the-art counterparts.

More information can be found at the following link:

https://www.frontiersin.org/journals/neuroscience/articles/10.3389/fnins.2024.1340164/full