Two new accepted contributions titled “Accelerating BPTT-Based SNN Training with Sparsity-Aware and Pipelined Architecture” and “A Low-Power Level-Crossing Analog-to-Spike Converter Intended for Neuromorphic Biomedical Applications”, have been accepted for presentation in the 2024 IEEE International Symposium on Circuits and Systems (ISCAS) to take place this coming May. Congratulations to CenBRAIN Neurotech's PhD students Chaoming Fang and Jinbo Chen for these achievements.、

Paper #1

C. Fang, F. Tian, J. Yang and M. Sawan, " Accelerating BPTT-Based SNN Training with Sparsity-Aware and Pipelined Architecture," IEEE International Symposium of Circuits and System (ISCAS), May 2024.

Abstract

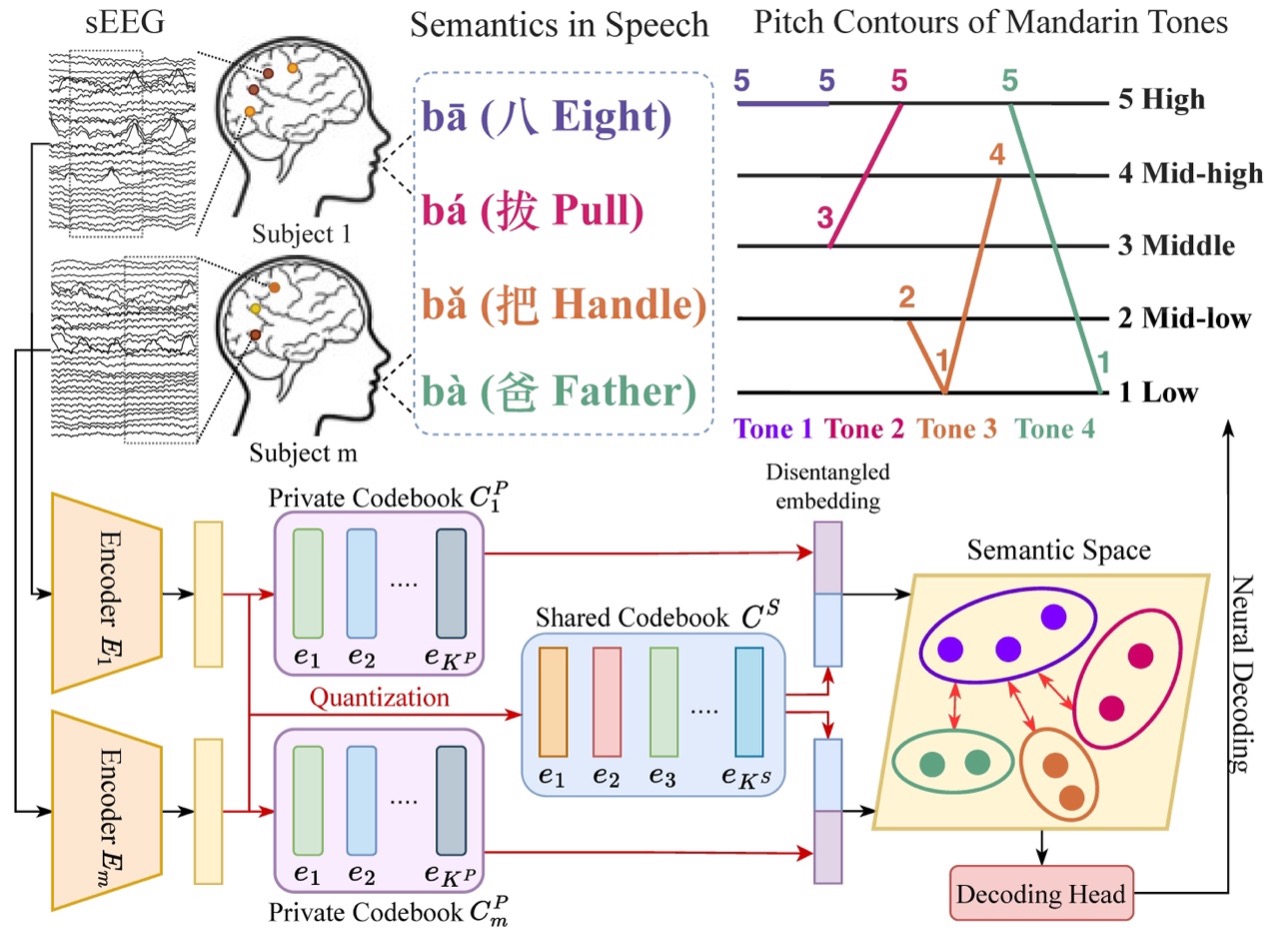

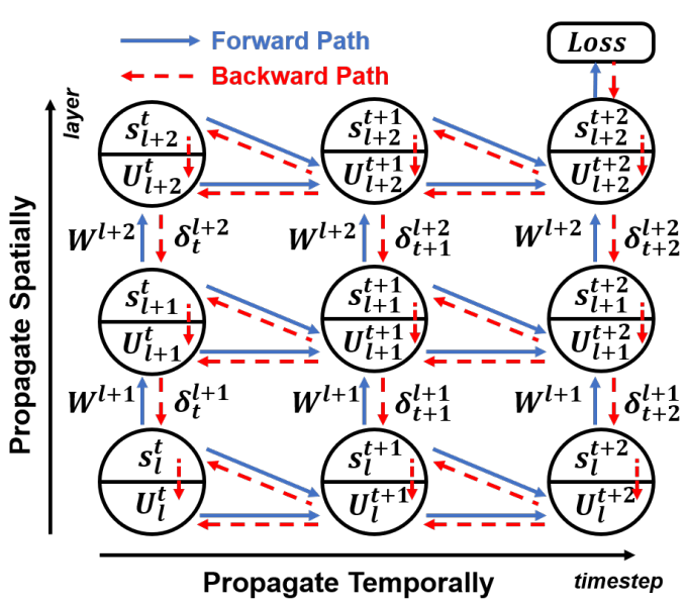

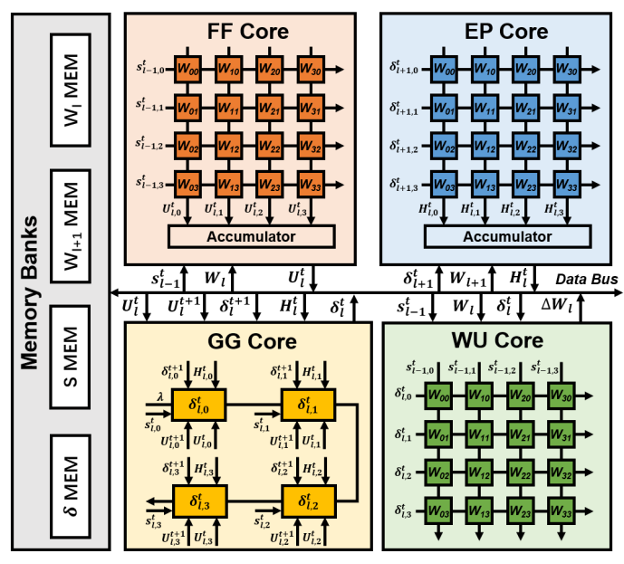

On-chip learning of Spiking Neural Networks (SNN) has been extensively researched to enhance adaptability and privacy protection, with Back-Propagation-Through-Time (BPTT) emerging as the top-performing method despite its resource-intensive nature. In this paper, we propose a dedicated training processor that accelerates the BPTT algorithm for SNNs. We analyze the bottlenecks and optimization opportunities in SNNBPTT and introduce novel techniques such as recalculation of membrane potentials to reduce redundant data movement. Additionally, we implement a pipeline architecture with heterogeneous computing cores to maximize hardware utilization and parallelism. Exploiting three types of sparsity in BPTT allows us to skip unnecessary computations and memory access, further optimizing performance. The proposed processor, implemented using 40nm CMOS technology, achieves simulation results with an advanced training energy efficiency of 0.86pJ/OP.

Fig. 1: Schematic of BPTT-Based SNN Training.

Fig. 2: SNN Backpropagation Training Accelerator Architecture Diagram

Paper #2

J. Chen, H. Wu, F. Tian, Q. Hou, S. Lin, J. Yang, and M. Sawan, “A Low-Power Level-Crossing Analog-to-Spike Converter Intended for Neuromorphic Biomedical Applications”, IEEE International Symposium on Circuits and Systems (ISCAS), May 2024.

Abstract

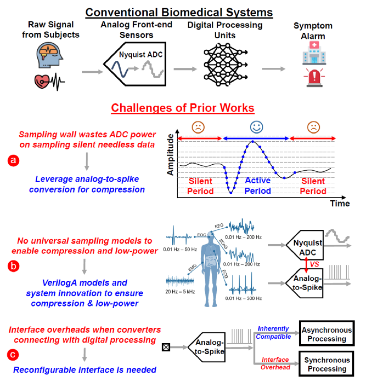

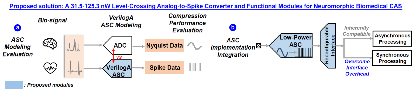

The increasing interests in building bio-signal recording and processing systems for personal healthcare applications have been hindered by the critical sampling energy consumption issues of conventional biomedical systems. To address these limits, we propose a comprehensive strategy centered around a low-power level-crossing analog-to-spike converter (LC-ASC). This strategy enables event-driven compressive sampling by leveraging signal sparsity, achieving lower average sampling rates than Nyquist sampling. Our strategy includes universal VerilogA LC-ASC models, evaluation tools, and a reconfigurable data interface for versatile digital processing. Specifically, we introduce an online open-source VerilogA LC-ASC model and compression performance calculation tools for evaluating its performance with different bio-signals. The implemented LC-ASC chip demonstrates very-low power consumption of 31.5-125.3 nW validated through chip measurements. Additionally, the proposed reconfigurable data interface ensures seamless integration with synchronous and asynchronous digital processing modules without sacrificing system-level performance. These advancements pave the way for energy-efficient neuromorphic biomedical circuits and systems.

Fig. 1: Conventional Biomedical Systems and Challenges.

Fig. 2: Proposed Solution: A 31.5-125.3nW Level-Crossing Analog-to-Spike Converter and Functional Modules for Neuromorphic Biomedical CAS.