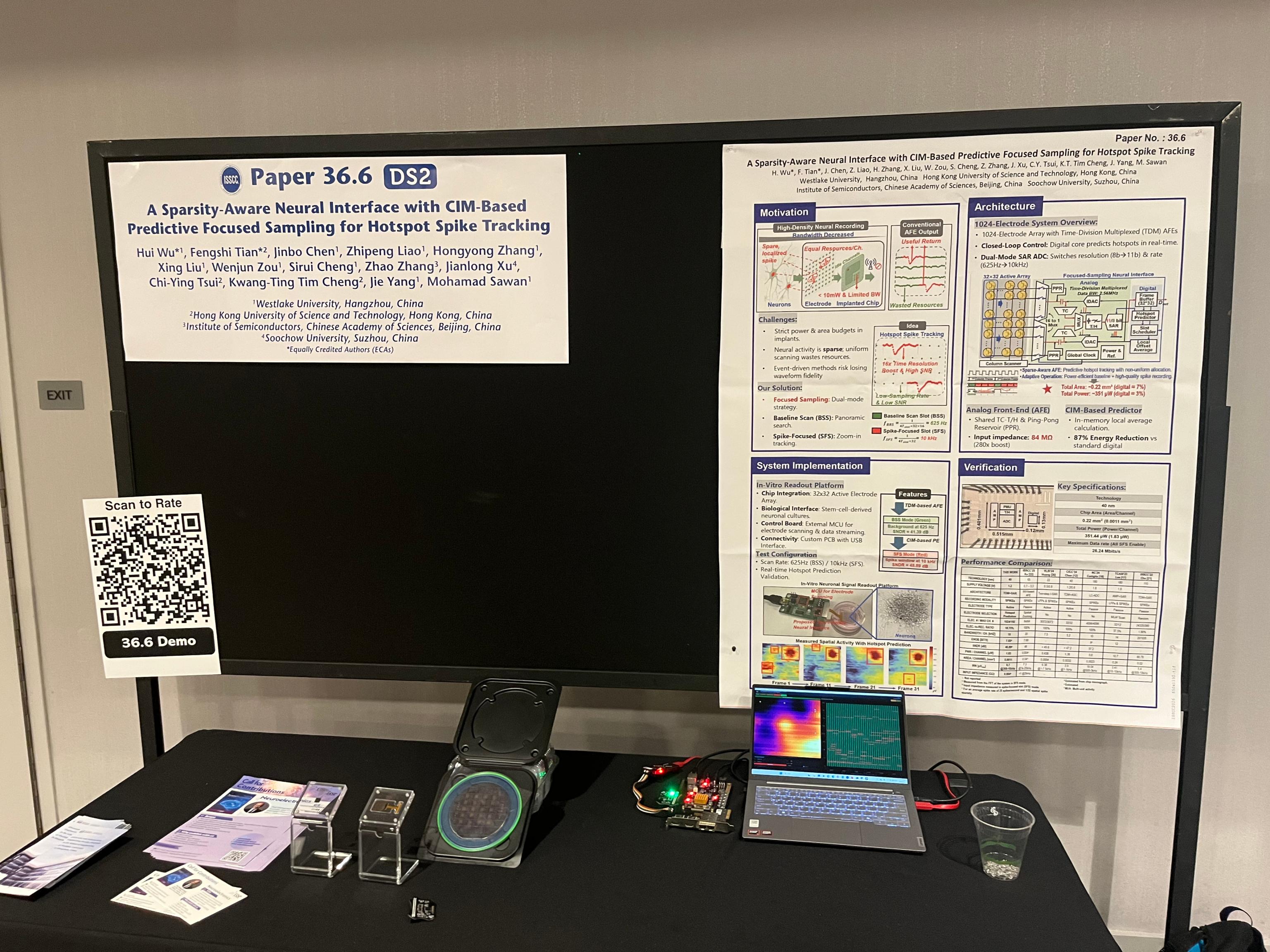

Recently, the IEEE International Solid-State Circuits Conference (ISSCC), a top-tier conference in the field of integrated circuit design, was held in San Francisco, USA. The team led by Chair Professor Mohamad Sawan, at the School of Engineering, Westlake University, presented their research contribution, titled "Sparsity-Aware Neural Interface with ClM-Based Predictive Focused Sampling for Hotspot Spike Tracking."

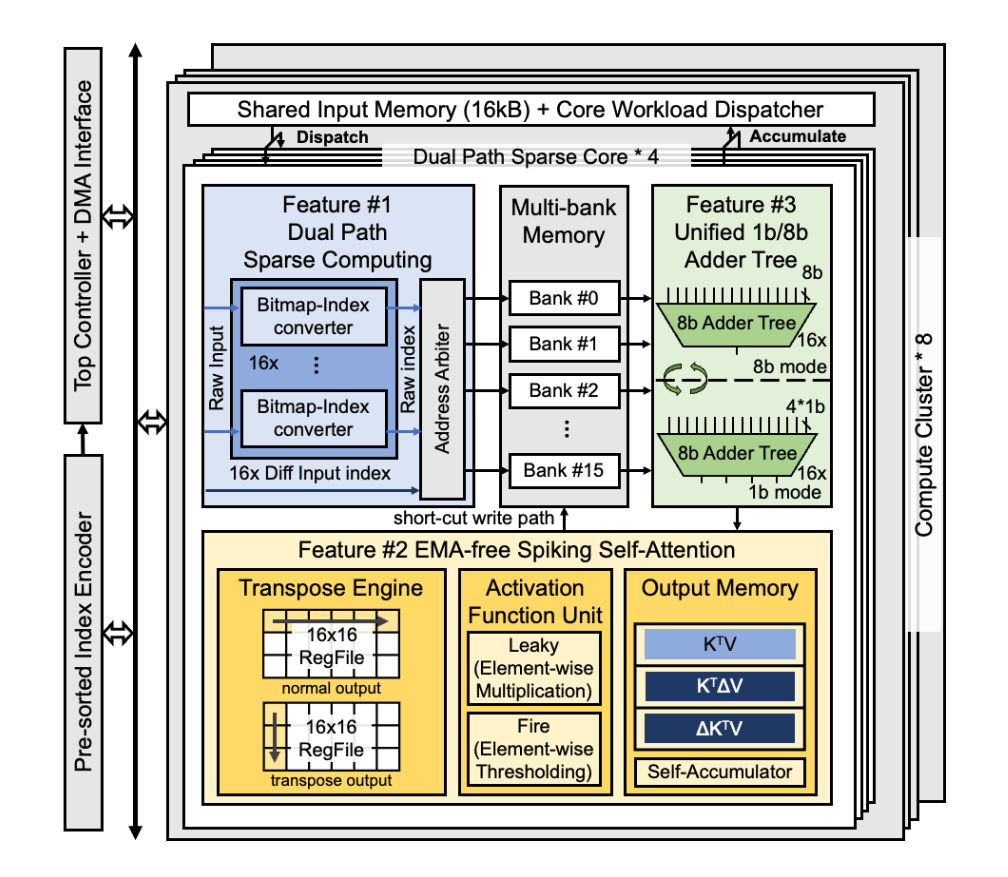

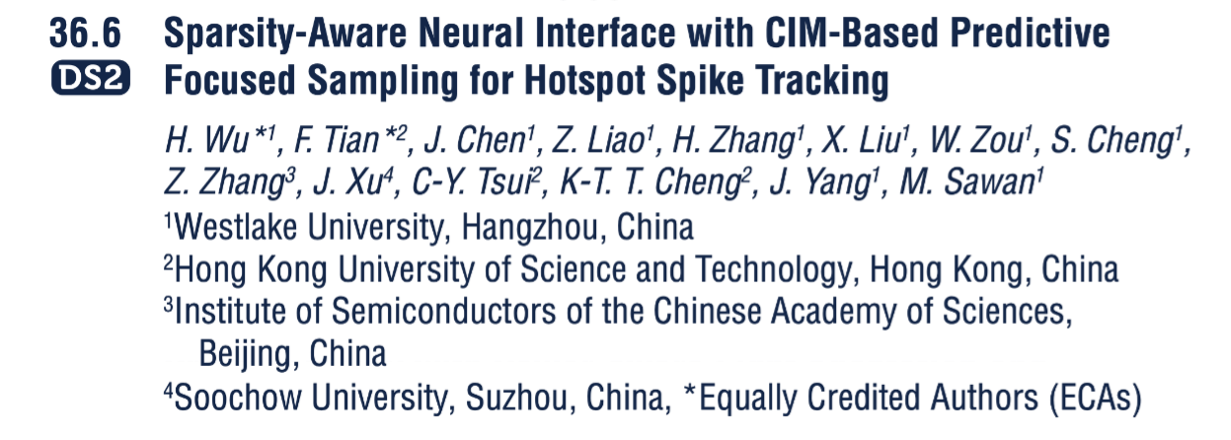

This work proposes a 1024-channel sparse sensing neural interface based on 40nm CMOS technology. By incorporating a real-time compute-in-memory engine for hotspot prediction, the system enables dynamic switching and collaboration between low-power panoramic scanning and high-fidelity spike tracking. Within a silicon area of only 0.22 mm², the interface achieves up to a 16x improvement in temporal resolution for active neural hotspots and demonstrates an energy efficiency of 1.83 µW/channel. This design effectively addresses the power and bandwidth wastage caused by the sparsity of neural activity in high-density neural recording. It provides a highly promising architectural paradigm for next-generation, long-term implantable brain-computer interface chips with ultra-high channel counts, marking a solid step towards deeper understanding of brain science, exploration of treatments for brain diseases, and the realization of high-performance brain-computer integration.

Hui Wu, a Ph.D. student at the CenBRAIN Neurotech, and former visiting student Fengshi Tian (Hong Kong University of Science and Technology) are the co-first authors of this research. Professor Mohamad Sawan, Chair Professor at the School of Engineering, Westlake University, is the corresponding author.

Abstract:

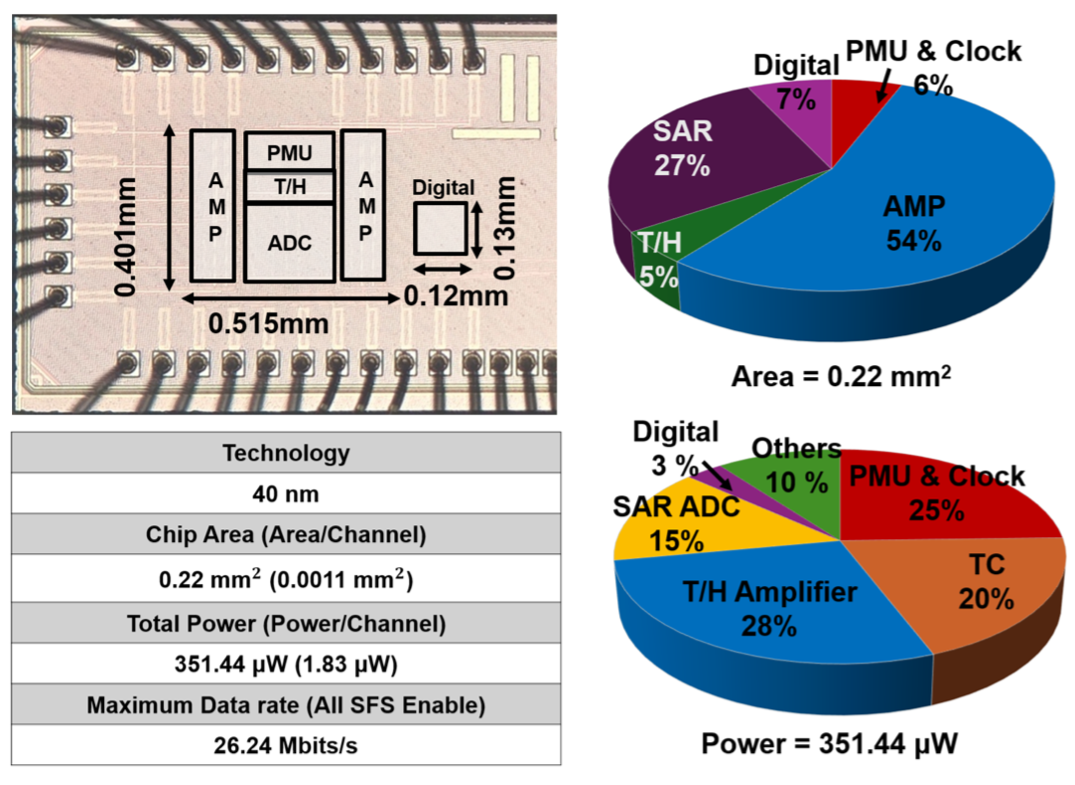

The development of high-density neural interfaces has long been constrained by the stringent power, area, and bandwidth limitations of implants. This problem is exacerbated by the mismatch between uniformly distributed hardware resources and the inherent sparsity and non-uniformity of neural activity. To address these challenges, this study presents a 1024-channel sparse sensing neural interface that employs a predictive focused sampling scheme to optimize resource allocation. By combining low-power panoramic scanning for hotspot prediction with high-fidelity spike tracking for active regions, the system effectively breaks the traditional trade-offs among power, area, and bandwidth.

Figure 1: Micrograph of the 1024‑channel chip fabricated in 40 nm CMOS technology.

In its specific implementation, the architecture innovatively introduces a dual-mode scanning strategy, combining low-power 8-bit panoramic monitoring with high-fidelity 11-bit spike tracking. This strategy not only provides a 16-fold improvement in temporal resolution (up to 10 kHz) for active neural hotspots but also achieves a data compression ratio exceeding 5.33 times, significantly alleviating the wireless data transmission burden of implantable devices.

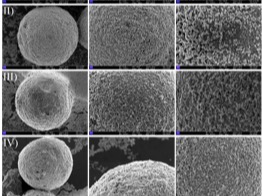

Figure 2: Results of in vitro neuron culture experiments, demonstrating successful digital hotspot prediction and the transition from panoramic mode to a high SNR focus mode.

This intelligent dynamic resource allocation is driven in real-time by a hotspot predictor built upon an energy-efficient compute-in-memory (CIM) core. This engine ensures robust tracking of dynamic neural activity patterns and exhibits inherent resilience to long-term electrode drift. Ultimately, by judiciously sharing a minimalist time-division multiplexed front-end across the 32x32 electrode array, the entire system is implemented within a mere 0.22 mm² silicon area, setting a benchmark for high integration density in thousand-channel neural recording implants.